R5550 シリーズ

インテリジェントパワースイッチIC

R5550 シリーズ

インテリジェントパワースイッチIC

- データシートダウンロード

- ECADモデル: 詳しく見る

-

拡大

:q

概要

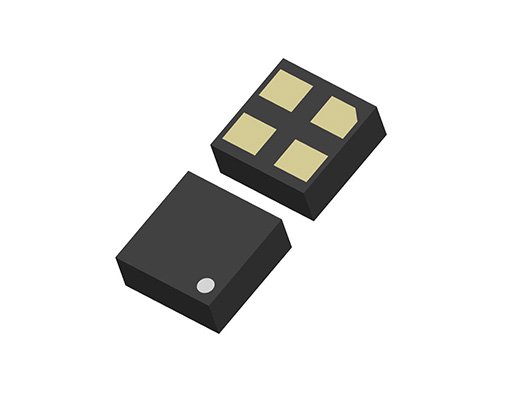

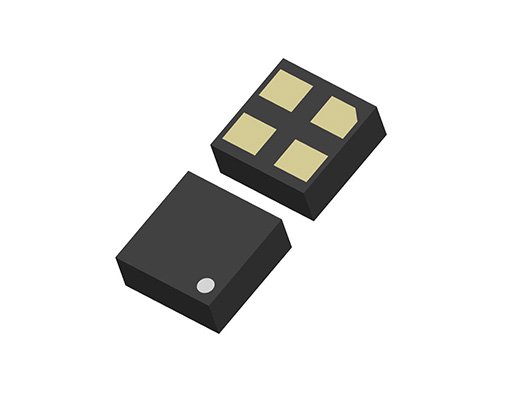

R5550 シリーズはCMOSのインテリジェントパワースイッチICです。過電流制限回路、低電圧誤動作防止回路(UVLO)を内蔵した電源ライン用の保護ICです。TYP. 180mΩの低オン抵抗Pch.ドライバトランジスタを内蔵し、低消費電流を実現しています。 R5550 は2種類の異なる過電流値と低電圧異常を検出することが出来ます。過電流を検出した場合は、設定された遅延時間後(10ms)にスイッチがOFFします。また、出力電流が出力電流制限値に達した場合は、直ちに電流を制限し、設定された遅延時間(1.33ms)の後、スイッチがOFFします。異常電圧を監視するVSENSE端子を持っており、異常電圧を検出した場合、設定された遅延時間(10ms)後に、スイッチがOFFします。異常検出後、エラーの原因が除かれた場合は自動的に復帰します。パッケージは、フリップチップと呼ばれる1mm角のDFN(PL)1010-4Fを採用しています。

仕様

| 民生 | |

|---|---|

| 入力電圧範囲 | 2.3 V ~ 5.25 V (6.0 V) |

| 動作温度範囲 | -40°C ~ 85°C (125°C) |

| 消費電流 | Typ. 2.6 µA (イネーブル, VSENSE = 2.0 V) |

| 出力電流 | 1 A |

| スイッチON抵抗 | 180 mΩ (VIN = 3.3 V, IOUT = 100 mA) |

| 内蔵FET | Pch |

| パッケージ | DFN(PL)1010-4F |

| センス端子検出電圧 | Typ. 0.5 V |

| センス端子検出電圧精度 | ±3% |

保護回路/ 機能

| TSD | Reverse | OCP | UVLO | OVLO | Soft Start | PGOOD | Auto Discharge | Reset |

|---|---|---|---|---|---|---|---|---|

|

|

機能説明

| TSD | サーマルシャットダウン機能 |

|---|---|

| Reverse Current Protection | 逆流防止機能 |

| OCP | 過電流保護機能 |

| UVLO | 低電圧誤動作防止機能 |

| OVLO | 過電圧誤動作防止機能 |

| Soft Start | ソフトスタート機能 |

| PGOOD | パワーグッド出力 |

| Auto Discharge | オートディスチャージ機能 |

技術資料

-

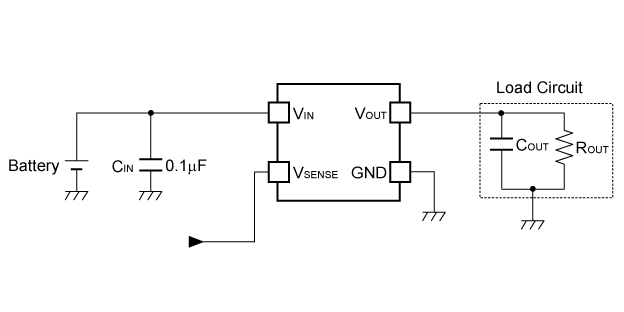

基本回路例

-

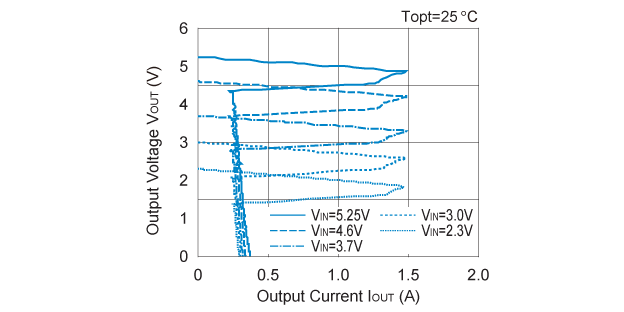

R5550KxxxA 出力電圧 対 出力電流

-

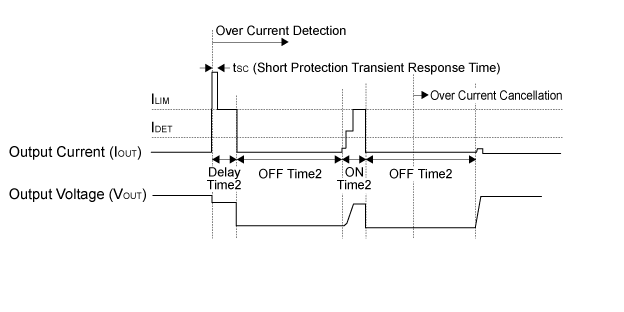

タイミングチャート 出力電流制限時

-

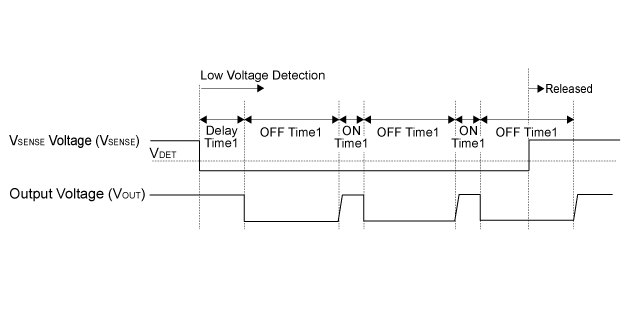

タイミングチャート 低電圧検出時

-

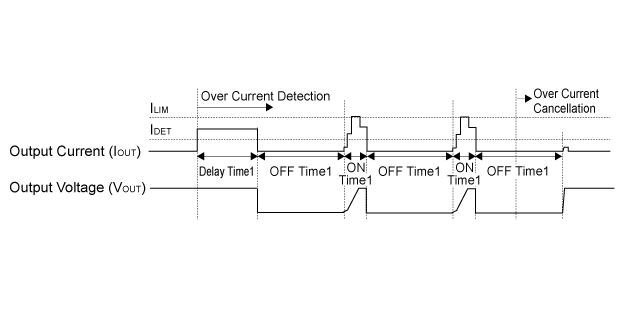

タイミングチャート 過電流検出時

品質・パッケージ

| 製品名 | 対応 | パッケージ情報 | マーキング情報 | 信頼性データ |

|---|---|---|---|---|

| R5550K001A-TR |

|

DFN(PL)1010-4F | R5550K | R5550K |

- 製品詳細はデータシートをご参照ください

- パッケージ外形図、テーピング仕様、テーピングリール外形図、許容損失、基板パット推奨寸法 (ランドパターン)、などはデータシートもしくは各パッケージをご参照ください

FAQ

ご購入とお問い合わせ

-

技術相談・テクニカルサポート