RP105 シリーズ

2電源 低電圧対応 400mA LDOレギュレータ

RP105 シリーズ

2電源 低電圧対応 400mA LDOレギュレータ

- データシートダウンロード

- ECADモデル: 詳しく見る

-

拡大

:q

:q

:q

概要

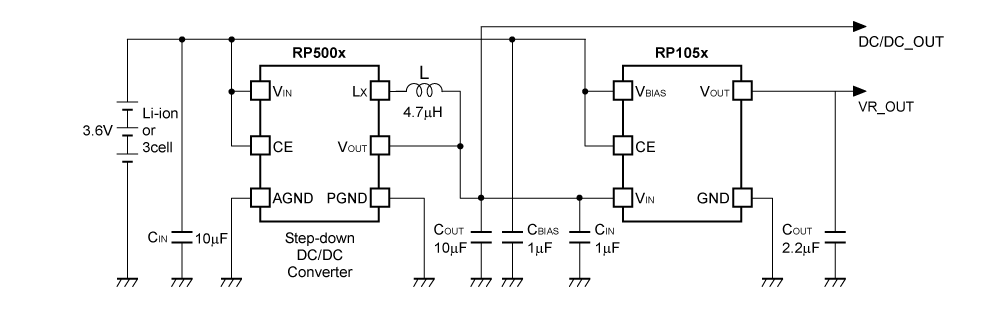

RP105 シリーズは2つの入力端子を持つCMOSの400mA出力可能なLDOレギュレータです。VBIAS端子に電源供給を受けることで入力電圧 MIN.0.9V、出力電圧 MIN.0.6Vという低電圧を実現しています。低電圧誤動作防止回路(UVLO)を内蔵し、入力電圧がVUVLOを下回ると出力をOFFします。0.4Ω (VSET=0.8V時) の低オン抵抗Nch.ドライバトランジスタを内蔵することで低入出力電圧差を実現し、負荷過渡応答特性をも向上させています。パッケージはSOT-23-5に加えて、1.2mm角のDFN(PL)1212-6 と DFN1212-5 もご用意しています。

仕様

| 民生 | |

|---|---|

| 入力電圧範囲 | VBIAS ·2.4 V ~ 5.25 V (6.0 V), VSET+1.6 V ~ 5.25 V (VSET ≥ 0.8 V) VIN ·B/Dバージョン: 0.9 V ~ VBIAS (VSET < 0.8 V), VSET + 0.1 V ~ VBIAS (VSET ≥ 0.8 V) ·E/Fバージョン: 0.9 V ~ VBIAS |

| 動作温度範囲 | -40°C ~ 85°C (125°C) |

| 消費電流 | Typ. 28 µA |

| スタンバイ電流 | Typ. 0.1 µA |

| 出力電圧範囲 | 0.6 V ~ 1.5 V (0.1 Vステップ) |

| 出力電圧精度 | ±1.0% (Ta = 25°C) |

| 出力電圧温度係数 | Typ. ±50 ppm/°C |

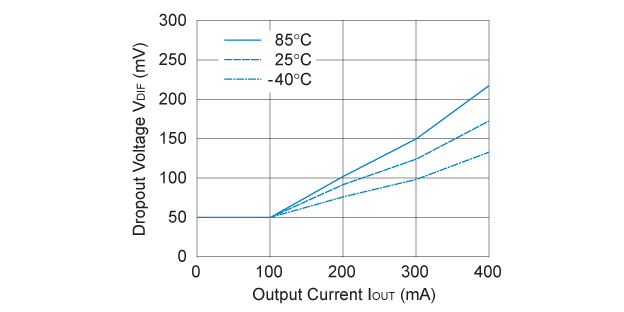

| 入出力電圧差 | DFN1212-5: Typ. 105 mV (IOUT = 400 mA, VSET = 1.5 V, VBIAS = 3.6 V) |

| 入力安定度 | Typ. 0.02%/V |

| リップル除去率 | Typ. 80 dB (f = 1 kHz, VIN Ripple) Typ. 50 dB (f = 1 kHz, VBIAS Ripple) |

| パッケージ | DFN1212-5, DFN(PL)1212-6, SOT-23-5 |

保護回路/ 機能

| TSD | Reverse | Current Limit | ISC | Inrush | ECO mode | Auto Discharge | External Driver | PGOOD | Soft Start |

|---|---|---|---|---|---|---|---|---|---|

|

|

|

機能説明

| TSD | サーマルシャットダウン機能 |

|---|---|

| Reverse Current Protection | 逆流防止機能 |

| Current Limit | 過電流保護機能 |

| ISC | 短絡電流制限機能 |

| Inrush Current Limit | 突入電流制限機能 |

| Constant Slope | コンスタントスロープ回路 |

| ECO mode | ECO機能 |

| Auto Discharge | オートディスチャージ機能 |

| External Driver | ドライバ用トランジスタ外付け |

技術資料

-

SPICEモデルダウンロード

SPICEシミュレーション モデルをダウンロードいただけます。 ダウンロード時には、myNISDへのログイン / 登録が必要です。

基本回路例

-

RP105x151x 入出力電圧差 対 出力電流

品質・パッケージ

| 製品名 | 対応 | パッケージ情報 | マーキング情報 | 信頼性データ |

|---|---|---|---|---|

| RP105Kxx1x-TR |

|

DFN(PL)1212-6 | データシート参照 | RP105K |

| RP105Lxx1x-TR |

|

DFN1212-5 | データシート参照 | RP105L |

| RP105Nxx1x-TR-FE |

|

SOT-23-5 | データシート参照 | RP105N-FE |

- 製品詳細はデータシートをご参照ください

- パッケージ外形図、テーピング仕様、テーピングリール外形図、許容損失、基板パット推奨寸法 (ランドパターン)、などはデータシートもしくは各パッケージをご参照ください

FAQ

ご購入とお問い合わせ

-

技術相談・テクニカルサポート