R3118 シリーズ

SENSE端子分離型 遅延機能付き 低電圧ボルテージディテクタ

R3118 シリーズ

SENSE端子分離型 遅延機能付き 低電圧ボルテージディテクタ

- データシートダウンロード

- ECADモデル: 詳しく見る

-

拡大

:q

:q

:q

概要

R3118 シリーズは遅延機能付きのCMOSボルテージディテクタICです。電源端子とは別に電圧監視用のSENSE端子を持っているため、電源が確保されている限り、リセット出力が不安定にならず"L"を保持することができます。検出電圧は0.6 Vから指定可能です。CD端子に外付けするコンデンサ容量によって解除遅延時間を設定可能です。パッケージはSOT-23-5 と、民生品ではSC-88A と1.2 mm角のDFN(PL)1212-6もご用意しています。

仕様

| 民生 | 車載 | |

|---|---|---|

| 動作電圧範囲 | 1.0 V ~ 6.0 V (7.0 V) | |

| 動作温度範囲 | -40°C ~ 85°C (125°C) | -40°C ~ 85°C (125°C) -40°C ~ 125°C (125°C) |

| 消費電流 | Typ. 0.4 µA (VSENSE ≥ +VDET, VDD = 6 V) センス抵抗に流れる電流は含まない |

|

| 検出電圧範囲 | 0.6 V ~ 5.0 V (0.1 Vステップ) | |

| 検出電圧精度 | ±1.5% (Ta = 25°C, -VDET_S ≥ 1.6 V) ±22.5 mV (-VDET_S < 1.6 V) |

|

| 検出電圧温度係数 | Typ. ±30 ppm/°C | |

| 解除遅延時間精度 | ±30% | |

| 出力形態 | CMOS, Nch Open Drain | |

| パッケージ | DFN(PL)1212-6, SC-88A, SOT-23-5 | SOT-23-5 |

技術資料

-

SPICEモデルダウンロード

SPICEシミュレーション モデルをダウンロードいただけます。 ダウンロード時には、myNISDへのログイン / 登録が必要です。

-

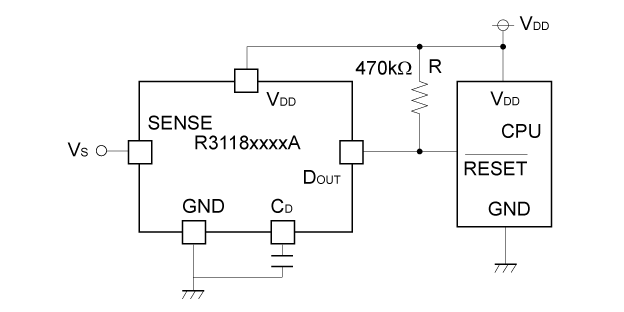

基本回路例 R3118xxxxA CPUリセット回路 (Nch オープンドレイン出力)

R3118xxxxA のVDD 端子電圧とCPU のVDD 端子電圧が等しい場合

-

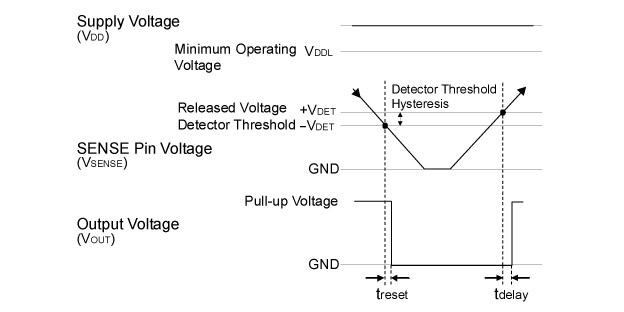

R3118xxxxA タイミングチャート

-

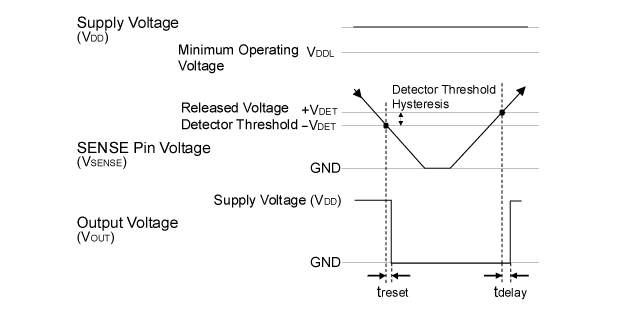

R3118xxxxC タイミングチャート

品質・パッケージ

- 製品詳細はデータシートをご参照ください

- パッケージ外形図、テーピング仕様、テーピングリール外形図、許容損失、基板パット推奨寸法 (ランドパターン)、などはデータシートもしくは各パッケージをご参照ください

FAQ

ご購入とお問い合わせ

-

技術相談・テクニカルサポート