同相信号除去比 CMR(Common mode Rejection Ratio)

1.同相信号除去比 CMR(Common mode Rejection Ratio)

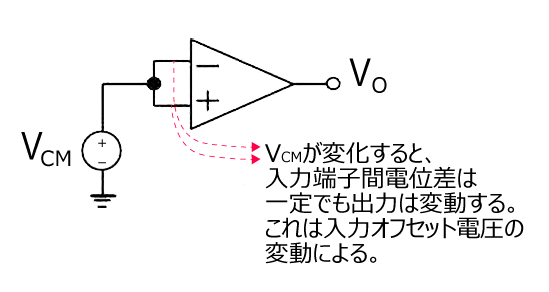

図1の回路では、同相入力電圧VCMが変化しても両入力端子には同電位が印加されるため、理想オペアンプであれば、出力は変動しません。しかし、実際のオペアンプでは、VCMの変化により出力電位が変動します。これは、同相入力電圧の変化により入力オフセット電圧VIOが変動するためです。同相信号除去比CMRはその特性を示しています。

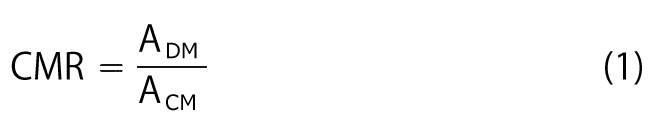

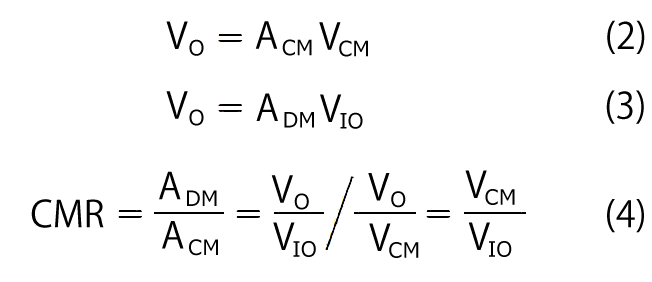

CMRの定義を式(1)に示します。出力VOは、同相利得ACMと同相入力電圧VCMを使えば式(2)で表され、差動利得ADMと入力オフセットVIOを使えば式(3)で表されます。式(1)、(2)、(3)よりCMRは式(4)のように書き換えられます。これより、CMRは同相入力VCMの変化と入力オフセット電圧VIOの変動の比であると言えます。

図1 同相信号を入力した場合の動作

ここで、ACMは同相利得、ADMは差動利得

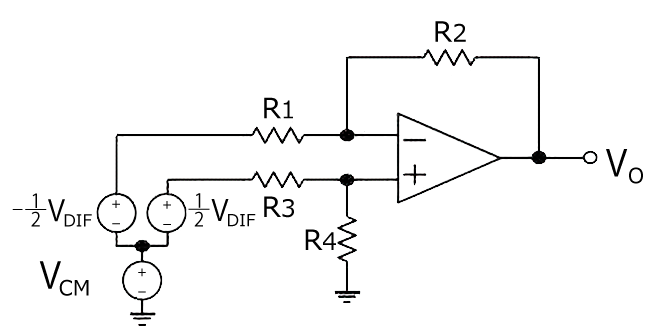

2.差動増幅回路

図2に示した差動増幅回路では、CMR特性が特に重要です。この回路は同相ノイズに対して有効ですが、その特性は、オペアンプのCMRだけではなく、差動利得、抵抗ばらつきが絡みます。差動増幅回路の特性を最大限引き出すために、これらのパラメータの関係性を解説していきます。

2.1 差動増幅回路のCMR

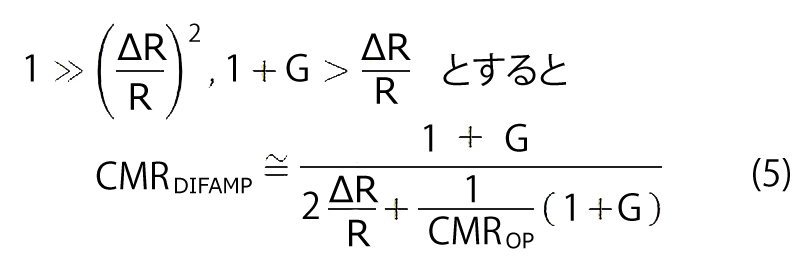

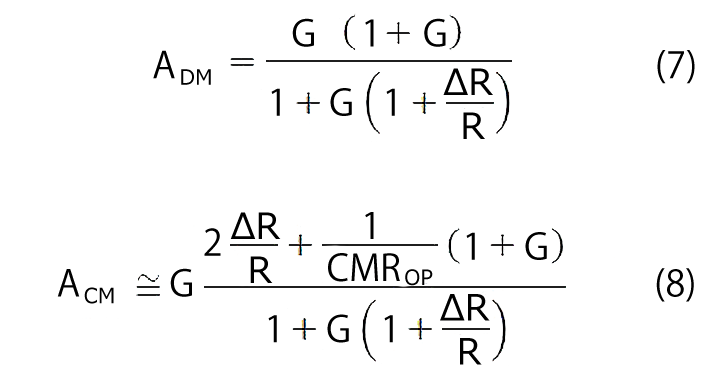

差動増幅回路のCMRは、オペアンプのCMR、抵抗比の設計値、抵抗ばらつきを用いて式(5)で表されます。

ここで、CMRDIFAMP は差動増幅回路のCMR、CMROPはオペアンプのCMR、Gは抵抗比の設計値、 は抵抗のばらつき

は抵抗のばらつき

2.2 差動増幅回路のCMR特性例

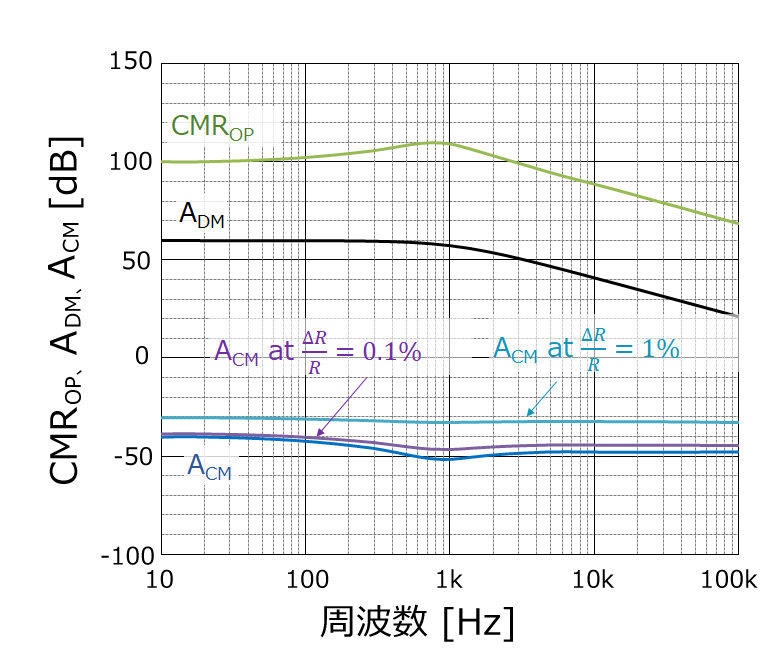

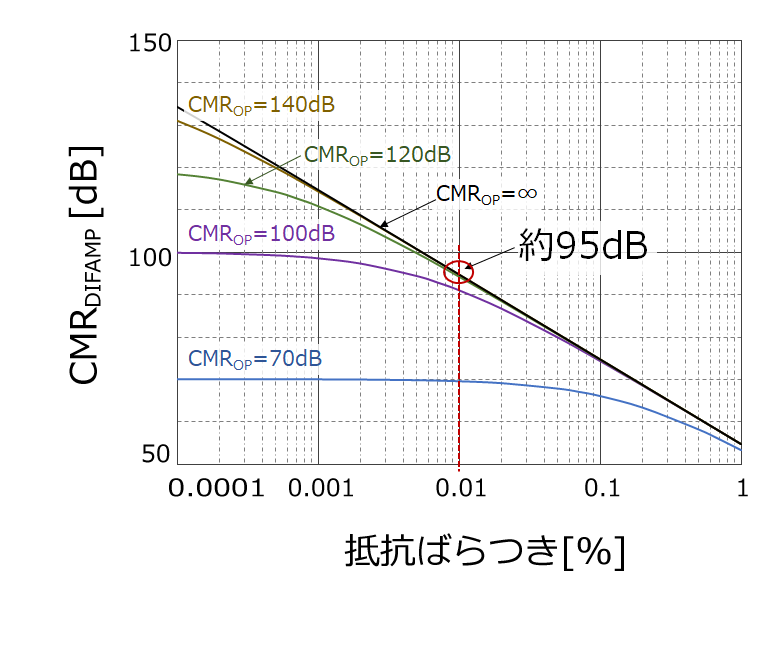

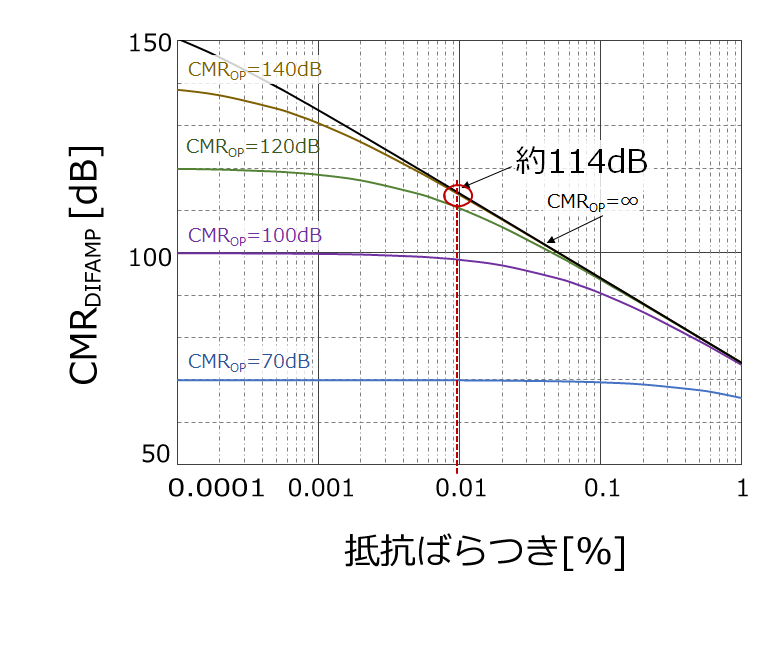

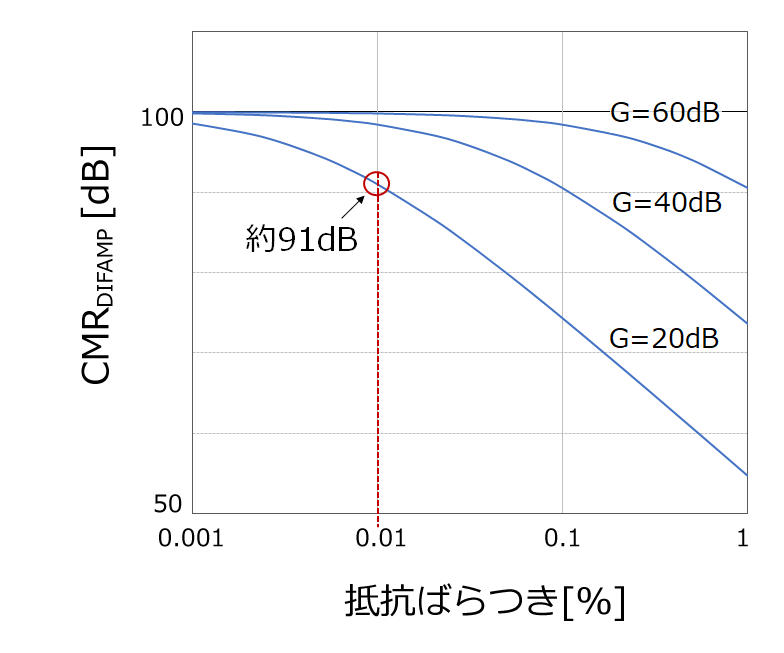

式(5)から導いた差動増幅回路の特性例を図3, 4に示します。

図3 G=20dB(抵抗比の設計値=10倍)

CMROP=100dBの特性をみると、抵抗ばらつき0.1%では、オペアンプのCMRが100dBにもかかわらず差動増幅回路のCMRを表すCMRDIFAMPは約74dBです。抵抗精度が高くなるにつれ、オペアンプのCMRの100dBに近づきますが、100dBを得るためには0.001%程度の超高精度が必要となることが判ります。又、CMROP=70dBの特性は、100dBと比較するとCMR値は低くなります。CMRDIFAMP=70dBは抵抗精度0.01%で得られますので、CMROP=70dB(最小値)のNJM2904Cを選択する場合、抵抗0.01%を超える精度は過剰品質となります。次に、CMROP=120dB、140dBの特性をみると、抵抗精度が高ければCMRDIFAMPは改善しますが、抵抗精度が低くなるにつれ、CMROP=100dB、70dBとの差が小さくなります。CMROP=∞の特性を黒の線で示します。この線は各抵抗精度の理論限界を示しており、0.01%の時は約95dBが最大値となります。

図4 G=40dB(抵抗比の設計値=100倍)

理論限界値は、G=20dBと比較すると約20dB高くなり0.01%のときCMRDIFAMP≒114dBです。抵抗比Gは、差動利得の設計値を意味しますので、他の要求仕様により設定される場合があります。そのようなケースでは、オペアンプ、抵抗精度を適切に選択し、目標のCMRDIFAMPを実現します。

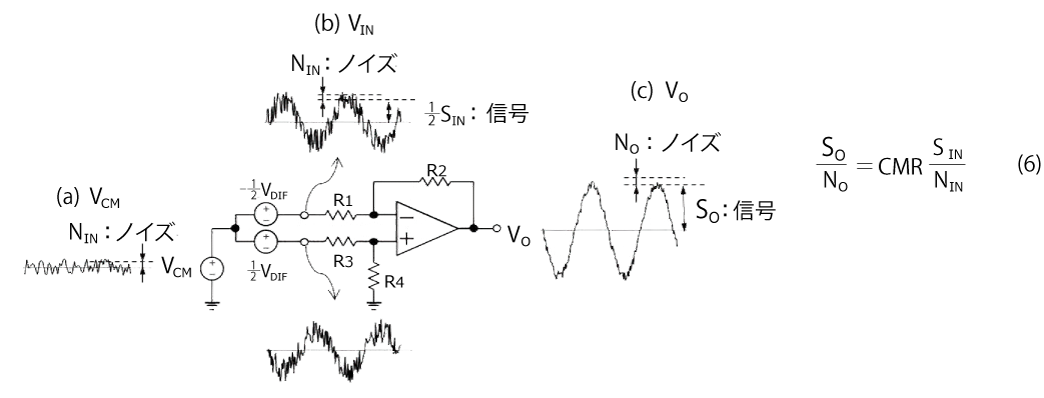

2.3 CMRとSN比

図5の差動増幅回路に同相ノイズVCM(ノイズレベルNIN)が入力され、差動信号としてVDIF(信号レベルSIN)が入力されてとすると、入力と出力のS/Nには、式(6)の関係があります。これより、出力のS/Nは入力のS/NよりもCMRにより改善されることが判りますので、同相ノイズに有効と言えます。

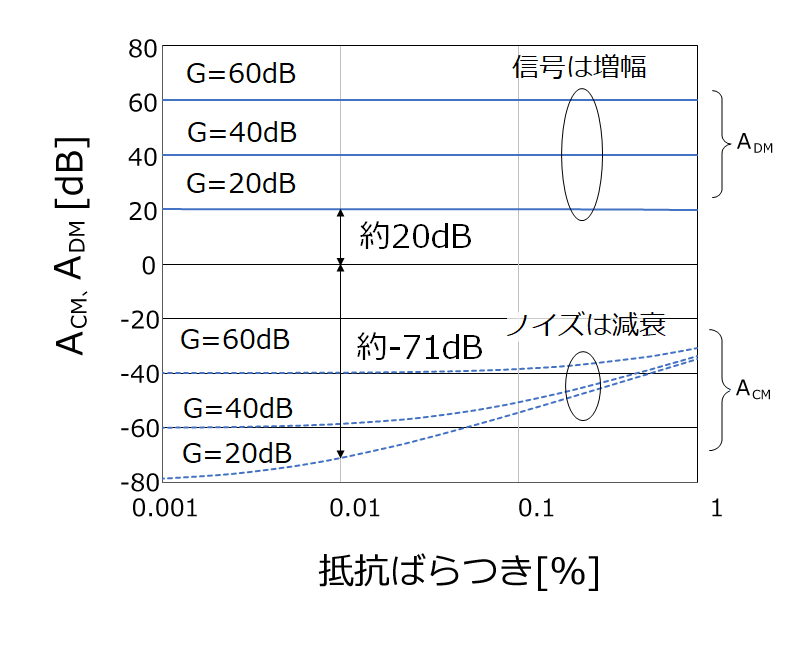

式(5)により求めた差動増幅回路のCMRの特性を図6に示します。また、式(7)、(8)により求めたACM、ADMの特性を図7に示します。この2つの特性例により差動増幅回路のCMRを表すCMRDIFAMPとS/Nの改善の関係を調べていきます。

例として、G=20dB、CMROP=100dB、抵抗ばらつき0.01%の条件を取り上げます。図6ではCMR≒91dBです。図7ではADM≒20dBのため、入力信号が約20dB増幅され出力信号となります。また、ACM≒-71dBであり、入力のノイズレベルが約-71dBで減衰されます。従って、出力のS/Nは約91dB改善されことになり、図6のCMR値と一致します。

このようにS/Nの改善は、信号レベルがADMで増幅され、ノイズレベルがACMで減衰されるためです。なお、抵抗比Gを大きくするとS/Nは良くなりますが、ノイズレベルも大きくなることに注意が必要です。

2.4 出力ノイズレベルの計算

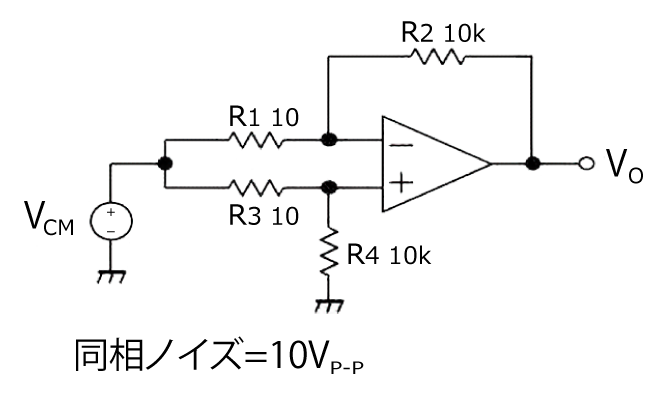

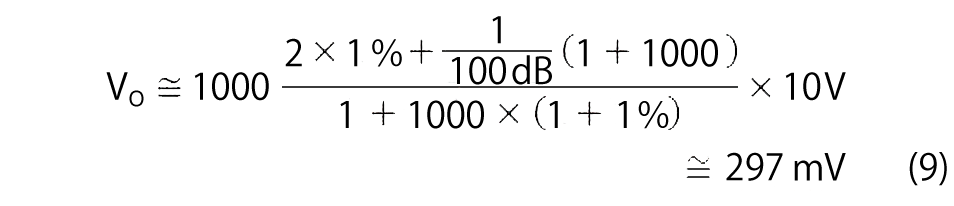

図8に示した回路の出力ノイズレベルを式(8)を用いて計算します。条件を代入して求めると約297mVとなり、入力の10Vに比較して約1/34に減衰します。

例題抵抗のばらつきΔR/R=1%

条件:CMROP=100dB、G=1000

2.5 CMRの周波数特性

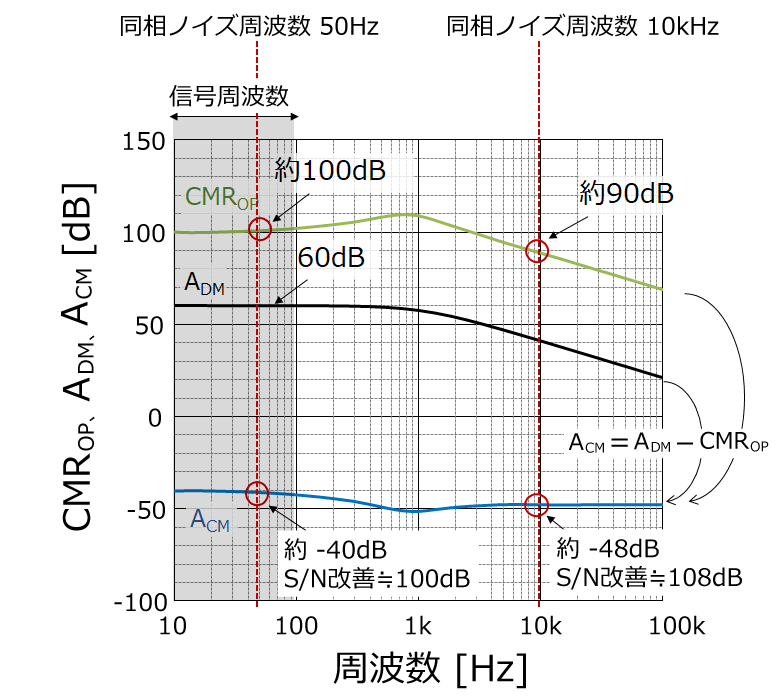

上記で説明したCMR値はDC特性です。しかし、実際の信号、ノイズは主にAC特性です。ここでは上記のDC特性の考え方をベースにAC特性へ展開する方法を示します。図9にオペアンプのCMR、差動利得ADM、同相利得ADMの各特性例を示します。ACMの特性は抵抗ばらつきを無視する場合、オペアンプのCMRとADMから容易に求める事ができます。

(1) S/N 改善レベル

例として、信号周波数は100Hz以下とします。

ノイズ周波数=50Hzのケース

ACM≒-40dB、ADM=60dBより、S/Nは約100dB改善し、CMROP≒100dBと同じになります。

ノイズ周波数=10kHzのケース

ACM≒-48dB、ADM=60dBより、S/Nは108dB改善されますが、CMROP≒90dBとは異なります。

このように信号周波数とノイズ周波数が異なると、S/N改善レベルはオペアンプのCMRとは異なります。ノイズには様々な周波数があり、どの周波数が支配的であるかを見極め、該当する周波数のACMにより計算をします。

(2) ACM特性

抵抗ばらつきを考慮したACM特性を求めるためには、式(8)を使います。例として、抵抗ばらつき0.1%と1%のACM特性例を図10に示します。抵抗ばらつきが大きくなるとACMの減衰量が減り、S/N改善レベル小さくなりますので、注意が必要です。