入力換算雑音電圧(en)

1.入力換算雑音電圧enの目的

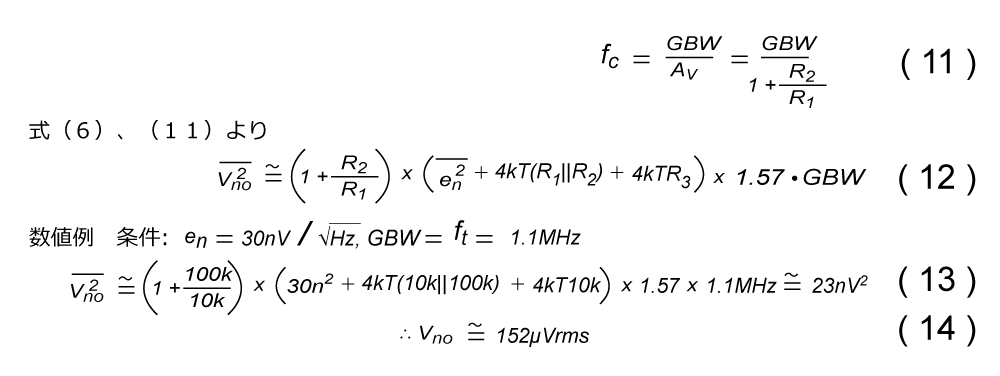

入力換算雑音電圧enは、オペアンプの内部から発生する雑音電圧を入力に換算したものです。

このenを使うことにより、様々な電圧利得、応用回路でオペアンプの出力雑音を求める事が出来ます。

図1 入力換算雑音電圧enの目的

2.入力換算雑音電圧enの意味

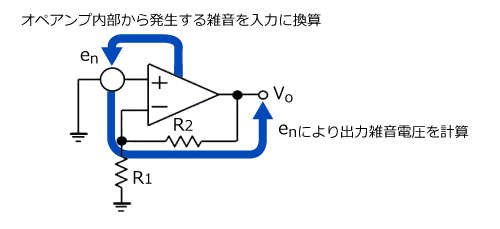

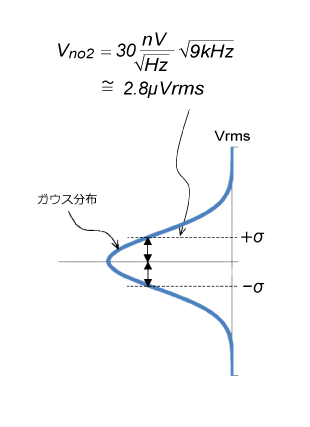

入力換算雑音電圧はランダムな値を示しますので、統計的な考え方が必要となります。入力換算雑音電圧は多くの場合、図2に示すガウス分布として考えることができ、スペックの30nV/√Hzは分布の1シグマになります。従って約68%は30nV/√Hz以下になりますが、約32%は30nV/√Hzを超えることをこのスペックは示しています。

| 項目 | 記号 | 条件 | 最小 | 標準 | 最大 | 単位 |

|---|---|---|---|---|---|---|

| 入力換算雑音電圧 | en | f=1kHz, RS=100Ω, V+=30V | - | 30 | - | nV/√Hz |

図2 入力換算雑音電圧の分布

3.入力換算雑音電圧の周波数特性

オペアンプの代表的な2つの雑音を示します。

- 3.1 白色雑音(ホワイトノイズ)

- 周波数によらず一定の領域の雑音は白色雑音です。電気的特性の入力換算雑音電圧は、この領域の雑音を示すのが一般的です。NJM2904Cのen=30nV/√Hzは、f=1kHzで規定されています。なお、白色雑音はガウス分布に従います。

- 3.2 1/f 雑音

- 周波数が低くなるにつれ雑音レベルが上昇します。この領域の雑音を1/f 雑音と呼びます。白色雑音と1/f 雑音の漸近線の交点の周波数を、1/f 雑音のコーナー周波数と言います。この雑音はガウス分布ではありませんが、システムの信号周波数が数十kHz、数百kHzと帯域が広ければ、白色雑音が支配的となりますので、多くの場合雑音全体としてはガウス分布に従うとして扱えます。もちろん、信号周波数が低周波領域に限定したシステムでは1/f 雑音が重要となります。

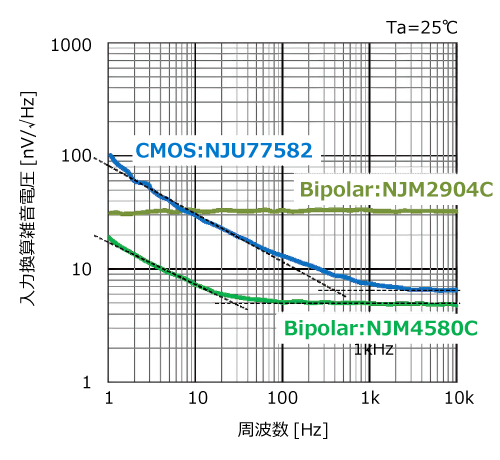

図3 入力換算雑音電圧の周波数特性例

4.Bipolar製品とCMOS製品の差異

オペアンプの周波数特性例を図4に示します。

- • Bipolar製品

(NJM4580C) - 1/f 雑音のコーナー周波数は数十Hzとなっています。

- • Bipolar製品

(NJM2904C) - フラットな周波数特性となっています。30nV/√Hzと白色雑音のレベルが高く、コーナー周波数は1Hz以下と考えられます。

- • CMOS製品

(NJU77582) - コーナー周波数はバイポーラ製品より一桁高くなっています。一般的にCMOS製品は、バイポーラ製品と比較すると低周波領域の雑音が大きくなりますので、低周波領域でCMOS製品を選択する場合は、1/f 雑音に留意する必要があります。

図4 Bipolar製品とCMOS製品の1/f雑音の差異

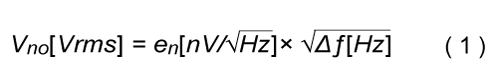

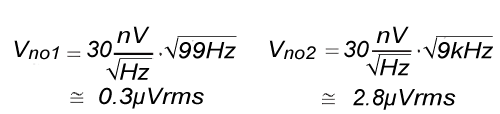

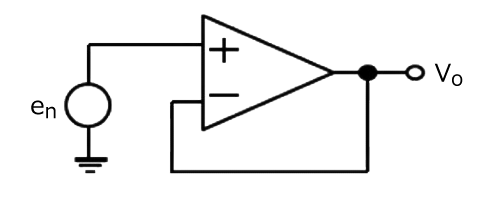

5. ボルテージフォロワの出力雑音電圧

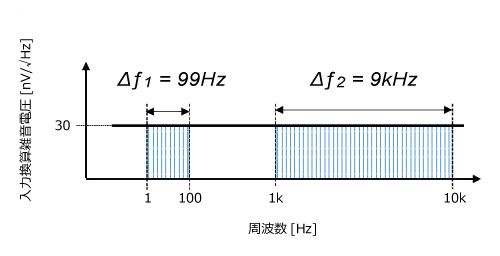

ボルテージフォロワの出力雑音電圧の計算方法を式(1)に示します。入力換算雑音電圧に帯域の平方根を乗ずる事により、必要な周波数帯域の雑音電圧を求める事が出来ます。図6の2例より、帯域が広くなると出力雑音電圧が大きくなっている事がわかります。

図5 ボルテージフォロワの出力雑音計算

図6 入力換算雑音電圧と周波数帯域

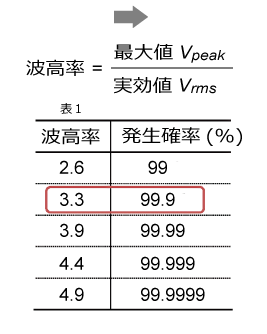

6.雑音波形の最大値

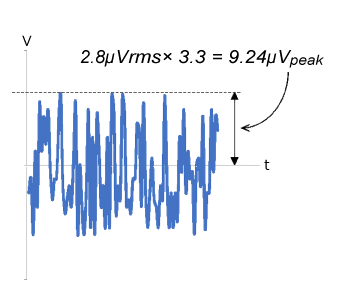

雑音電圧の最大値Vpeakは、実効値Vrmsに波高率を乗ずる事により求めることができます。サイン波であれば実効値に√2をかけて求めることができますが、雑音の場合は表1に示すように確率を考慮する必要があります。発生確率を99.9%を選択すると2.8μVrmsは3.3をかけて9.24μVpeakとなります。99.9%がこの値に収まることになります。

図7 雑音電圧の分布

図8 オシロスコープで観測した雑音電圧波形の例

出力雑音計算

1.雑音計算回路

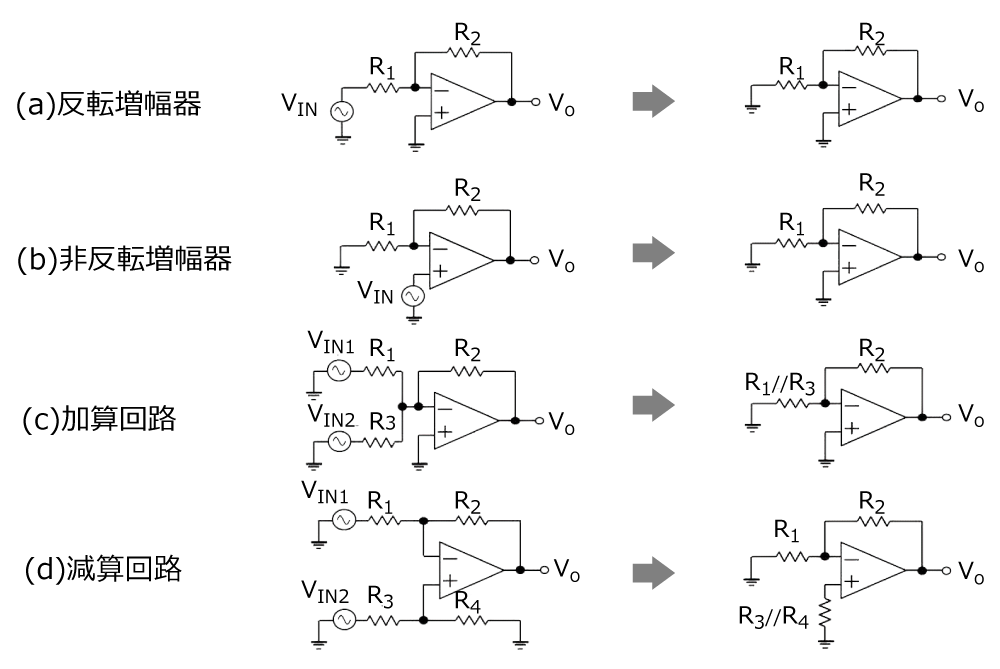

図1の4つの応用回路を例に雑音計算方法を解説します。雑音計算回路は、入力信号源を取り除き、抵抗値をまとめると図2の様に書き換えられます。

図1 オペアンプの応用回路例

図2 VINを削除

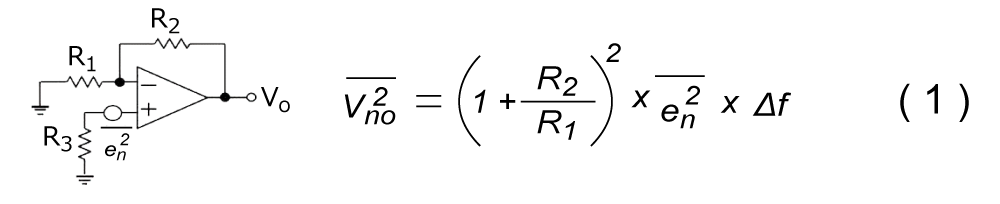

図2の回路は抵抗値を適切に変更することにより、図3の回路と等価となります。ここで、入力換算雑音電圧enの二乗を+入力端子に挿入します。 このオペアンプの入力換算雑音電圧を信号源と捉えると非反転増幅器と同じ形式となります。従って出力雑音は式(1)で与えられます。 雑音計算では、二乗平均値を用いるため、抵抗比も二乗します。

図3 オペアンプの雑音計算回路

2.抵抗の熱雑音

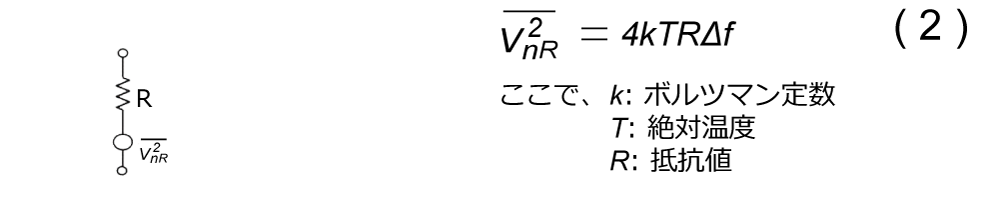

抵抗は受動素子ですが、熱雑音を発生します。抵抗の熱雑音は式(2)で与えられます。

図4 抵抗の熱雑音

3.出力雑音計算式の導出

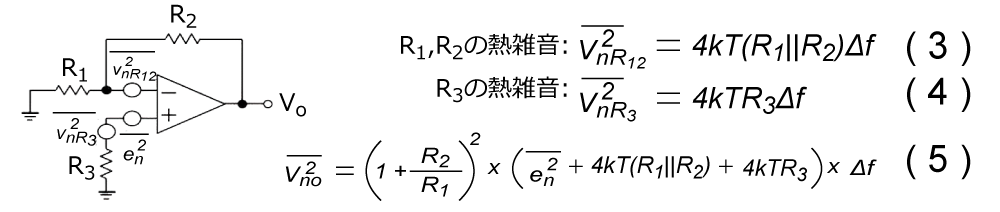

抵抗R1とR2の雑音は、図5に示す様にオペアンプの入力端子に移動し、 とすると計算がし易くなります。

とすると計算がし易くなります。

は、R1とR2の並列抵抗値の雑音と等価となり式(3)で表されます。抵抗の雑音とオペアンプの入力換算雑音は、それぞれ独立しているため加算し、電圧利得と帯域を乗じれば出力雑音となります。

は、R1とR2の並列抵抗値の雑音と等価となり式(3)で表されます。抵抗の雑音とオペアンプの入力換算雑音は、それぞれ独立しているため加算し、電圧利得と帯域を乗じれば出力雑音となります。

図5 オペアンプと抵抗の雑音計算回路

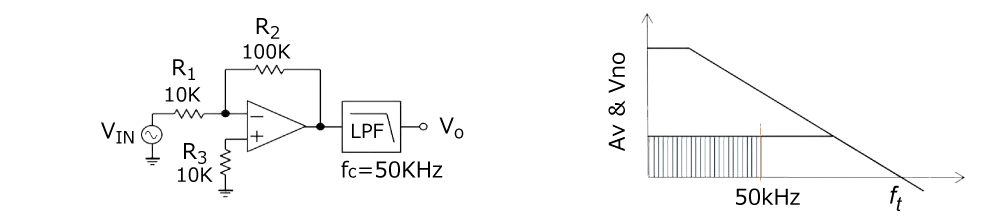

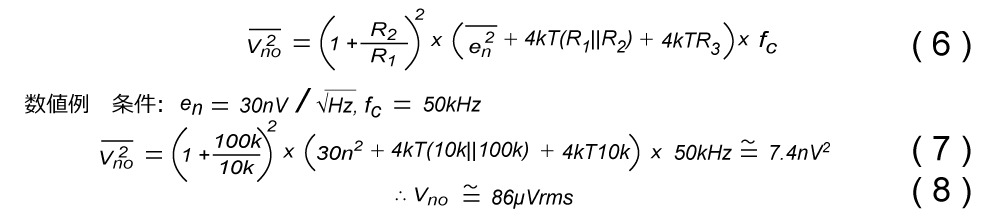

4.出力雑音計算例:出力フィルタ有

ローパスフィルタが接続されている回路では、帯域はフィルタの遮断周波数で決まるため、出力雑音は式(6)により求める事ができます。

図6 フィルタが接続されている回路

図7 電圧利得と出力雑音の周波数特性

5.雑音最適化設計のひとつの手法

雑音の最適設計、低雑音設計のひとつの手法を示します。オペアンプの雑音を抵抗値に換算することにより、各雑音源の比較が容易となります。オペアンプの雑音30n2は、4kTで割ると約54kΩになります。そうすると式(7)は式(9)のよう書き換えられます。他の抵抗値と比較するとオペアンプの雑音が支配的な事がわかります。

雑音レベルを下げるため、10nV/√Hzのオペアンプに変えたとします。そうすると約6kΩの雑音となります。この状態から更に低雑音にするにはオペアンプよりも抵抗値を下げた方がよい事がわかります。雑音レベルや比率を求めるだけならSPICEシミュレーションを使えば出来ますが、具体的な最適値を求めるには、式を立てた方が良い場合があります。

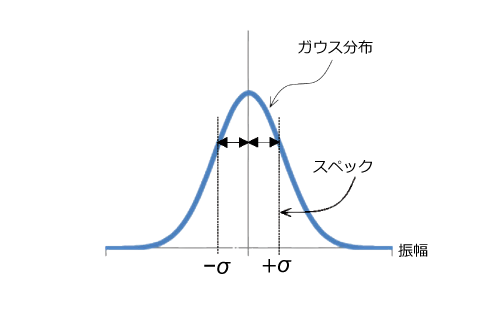

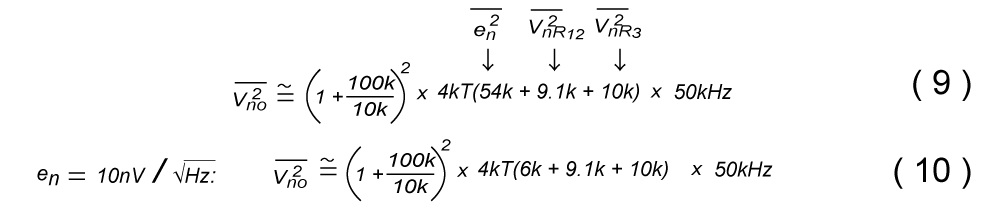

6.出力雑音計算例:出力フィルタ無

オペアンプ単体の場合、図9に示す様に遮断周波数より高い周波数で利得が減少するため、帯域計算が問題となります。電圧利得が-6dB/octaveの傾きで減少する回路では、fcに1.57倍を乗じた帯域と等価となります。

図8 オペアンプ単体回路

図9 電圧利得と出力雑音の周波数特性

遮断周波数fcは利得帯域幅積GBWと電圧利得から計算できます。