日清紡マイクロデバイス、OKIとアナログICの薄膜化と3次元集積化に成功

~ 既存のプロセスを用い、チップ面積を大幅削減 ~

~ 既存のプロセスを用い、チップ面積を大幅削減 ~

日清紡マイクロデバイス株式会社(代表取締役社長 吉岡 圭一)(以下 日清紡マイクロデバイス)は、沖電気工業株式会社(代表取締役社長 森 孝廣)(以下OKI)と共同で、アナログICの3次元集積に成功しました。

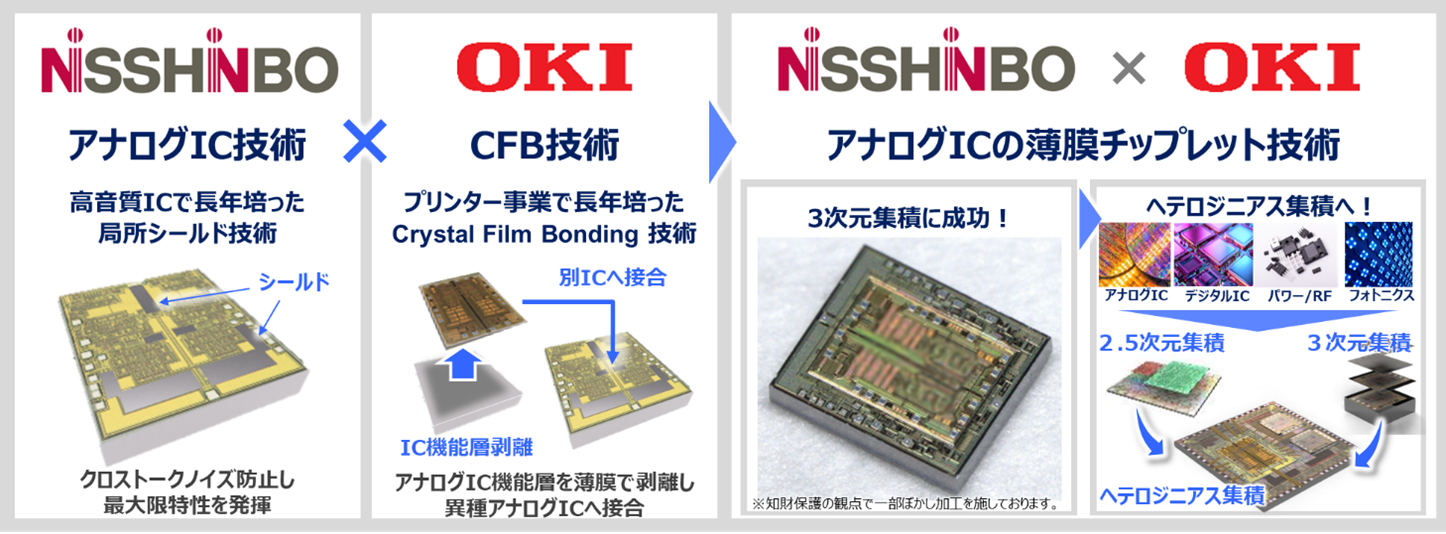

今回開発した3次元アナログICは、日清紡マイクロデバイスの局所シールド技術注1とOKIのCFB注2技術を用いて実現いたしました。両社は本技術を用いた製品開発を進め、2026年の量産化を目指します。

アナログICは、「0」と「1」を区別するデジタルICとは違い、信号強度自体に意味をもつため、回路内のトランジスター、抵抗等の素子ばらつきが特性面に大きな影響を与えます。そのため、素子ばらつきに影響を与える微細化には限界がありました。今回、開発に成功した技術は、レガシーファブ注3を活用して集積度を高めることが可能です。また薄膜化したアナログICはチップレット注4やヘテロジニアス集積注5へ適用出来ます。

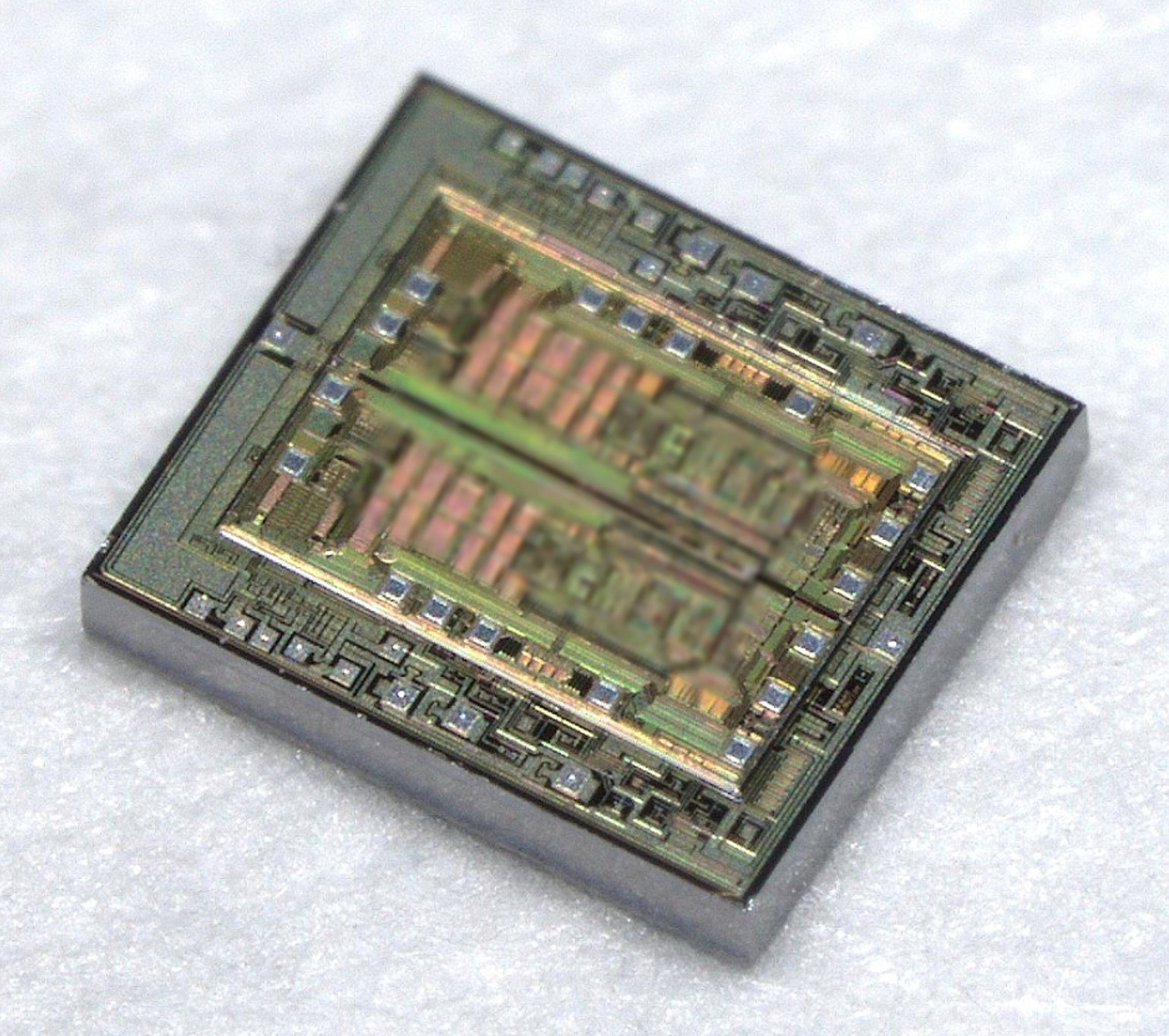

3次元アナログIC

薄膜アナログICが別のアナログICに接合された写真

知財保護の観点から一部にぼかし加工を施しています。

背景・課題

AI、自動運転や高度運転支援システム(ADAS)において、センシング技術の進化は重要な役割を果たしています。例えば、ADASにおいては、複数のセンサー(カメラ、ミリ波レーダーなど)から得られる多量なデータをAIで分析し、車両の動きや周辺環境の変化を瞬時に判断しています。車で使用されているセンサーは既に50個を超えており、設置場所の自由度、統合化による小型化が求められています。また、センサーからは微弱なアナログ信号が出力されるため、その信号を安定に、ノイズなく正確に捕らえる必要があり、アナログICにおいても小型化、高性能化の要求が高まっています。

しかし、アナログICを微細化して小型化しようとすると、その代償として、耐圧の低下やノイズの増加といった問題が発生します。この問題を解決するために、これまでは長期間にわたるプロセス開発や、多額の設備投資が必要でした。

そこで、アナログソリューションプロバイダー注6を目指す日清紡マイクロデバイスはアナログICにおいて、3次元集積に取り組んできました。

成果

日清紡マイクロデバイスが長年培ってきたアナログIC技術がOKIのCFB技術と融合することによって、アナログICの性能を維持したまま、積層により小型化を図る画期的な技術を開発しました。

2回路入りオペアンプ上に2回路入りオペアンプを積層した4回路入りオペアンプは、従来の4回路入りオペアンプに比べ、チップ面積を30%以上(当社比)削減できました。この方法により4層の積層を行えば、チップ面積を約1/4にすることも可能です。

さらに、積層部を薄膜化しているため、チップ厚もこれまでと同等で、既存半導体パッケージに実装することが可能です。

新技術の概要

このような実装が可能になったのは、局所シールド技術を用いたためです。この局所シールドとは、チップ全体にシールドを施さずに、上下チップ間の影響が及ぶ箇所にのみシールドを施し、回路機能を低下させることなく、信号干渉を抑える技術です。この技術を用いることにより、20Vppの高い電圧出力下においても、クロストークノイズ注7の発生を抑え込むことができました。

また、薄膜化により上下チップ間を従来の再配線プロセスによって接続できるため、接続パッドの最小化によるチップシュリンク化が実現できます。更に、高価なTSV注8を用いることなく、上下チップ間を電気的に接続することが可能です。

今後の展望

今後、両社は、本技術による新たな付加価値をもつ製品の開発を進め、パートナーリングやライセンシングも視野に2026年の量産化を目指します。

参考

本技術について2024年10月23日~24日までベルサール東京日本橋で開催される

「OKI WORLD 2024」にて、デモ展示を行います。

また、同展示会セミナーで詳細な説明を行います。

※「OKI WORLD 2024」(https://www.oki.com/jp/ad/ow2024/)セミナー「S-1」11:10~11:50

用語解説

- 注1:局所シールド技術

特定の回路のみをシールドする技術。これにより寄生容量を低減し、アナログ IC の性能を最大限に発揮しつつノイズを低減させます。回路とレイアウトの同時最適化が必要なため技術難易度が高い。 - 注2:CFB (Crystal Film Bonding)技術

半導体デバイス機能層を薄膜剥離し、異なる材料基板に分子間力で接合するOKIの独自技術。接着剤を介さない直接接合のため、接合間で電気・光・熱など伝搬でき、接合後の半導体プロセスが可能なため、異種材料・機能を統合した新たな半導体デバイスの創出に貢献する。 - 注3:レガシーファブ

既存の製造技術や設備。以前の世代のプロセス設備で、コスト効率が高いため現在も多くのアナログ IC で使用されている。 - 注4:チップレット

大規模な回路を機能毎に複数のチップに分割し、インターポーザ―と呼ばれる基板上に集積・搭載することにより大規模化して1パッケージに収める技術。 - 注5:ヘテロジニアス集積

異なる種類の複数のチップレットを1つのパッケージにまとめる手法。 - 注6:アナログソリューションプロバイダー

日清紡マイクロデバイスが提唱している豊富な製品ポートフォリオを生かしアナログ技術をコアにし半導体ユーザーの困り事を包括的に解決する メーカー。 - 注7:クロストークノイズ

ある伝送線路から別の伝送線路に対して電磁誘導によって発生するノイズ 。 - 注8:TSV(Trough Silicon Via)技術

シリコン基板に垂直な貫通孔を作り、層間接続を実現する 3 次元集積技術。 工程フローが多く、高価なプロセス。

リリース関連リンク

沖電気工業株式会社プレスリリース (https://www.oki.com/jp/press/2024/10/z24028.html)

OKI WORLD 2024 (https://www.oki.com/jp/ad/ow2024/)

- CFB は、沖電気工業株式会社の登録商標です。

- その他、本文に記載されている会社名、商品名は一般に各社の商標または登録商標です。

このニュースリリースの詳細 (PDF)

日清紡マイクロデバイス、OKIとアナログICの薄膜化と3次元集積化に成功 ~ 既存のプロセスを用い、チップ面積を大幅削減 ~

(新技術説明会資料)日清紡マイクロデバイスxOKIアナログIC x CFBの共創による新技術 ~「薄膜チップレット技術」 による 「3次元アナログIC」の実現~

報道関係者様へ

-

製品画像ダウンロード

ご利用条件:

画像として掲載されている画像データは、日清紡マイクロデバイス株式会社 (以下、当社) が著作権その他の権利を有しております。

画像は、各種報道機関が、当社および当社の各商品を紹介するためにのみご利用 (複製、アップロード、掲示、頒布、出版等を含む) いただけます。それ以外のご利用は、事前に当社の文書による許諾がない限り、禁止いたします。

このページに掲載されている内容は発表時のものです。既に販売終了になっている商品や、内容が異なっている場合があります。